Suis transistor ialah elemen asas peranti elektronik maklumat dan banyak peranti elektronik kuasa.

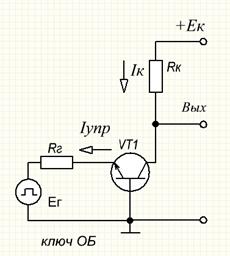

Dalam Rajah. 9.11a menunjukkan gambar rajah kekunci termudah dihidupkan transistor bipolar, disambungkan mengikut litar dengan pemancar sepunya, dalam Rajah 9.11 b terdapat gambar rajah voltan masukan, dan dalam Rajah. 9.11 V – voltan keluaran.

Mula-mula, mari kita lihat operasi suis transistor dalam keadaan mantap. Sehingga masa t 1, simpang pemancar transistor dikunci oleh voltan input negatif, transistor berada dalam mod potong.

Rajah 9.11. Skim suis termudah pada transistor bipolar dan gambar rajah operasinya

Dalam mod ini, I K = -I b =I K 0 (I K 0 ialah arus pengumpul terbalik), I E 0. Mengabaikan arus pengumpul terbalik kecil I K0, kita memperoleh i k = i b 0. Dalam kes ini, U R b U R k 0; U menjadi U 2; U ke E K. (Rajah 9.11 c).

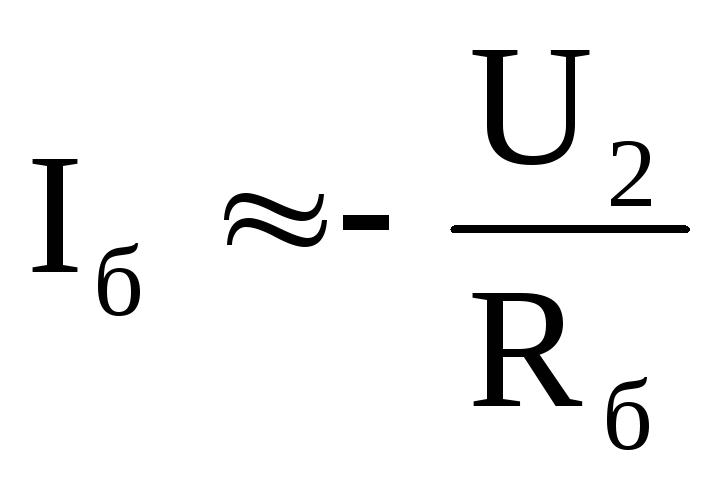

Dalam selang t 1 t 2, nilai rintangan R b dan voltan input U 1 dipilih supaya transistor berada dalam kawasan tepu, atau hampir dengannya.

Dalam mod ini, transistor dibuka dan hubungan berikut dipenuhi:

Oleh itu, potensi input (kawalan) rendah sepadan dengan potensi tinggi pada output suis dan sebaliknya. Mod operasi ini dipanggil songsang. Selalunya litar utama berfungsi antara satu sama lain dan kemudian voltan input (kawalan) akan mempunyai bentuk isyarat keluaran, yang bermaksud bahawa dengan mengambil kira kemungkinan gangguan input, parameter litar mesti dikira sedemikian rupa sehingga voltan input tidak melebihi nilai ambang tertentu. Sebagai contoh, untuk transistor silikon, pensuisan yang boleh dipercayai dipastikan dengan tahap 0.4 V. Pembukaan kunci transistor yang boleh dipercayai dipastikan dengan syarat hubungan berikut dipenuhi:  . Di samping itu, perlu diambil kira bahawa R K mesti dipilih supaya apabila transistor dibuka, arus pengumpul tidak melebihi maksimum yang dibenarkan untuk jenis transistor yang dipilih. Itu dia

. Di samping itu, perlu diambil kira bahawa R K mesti dipilih supaya apabila transistor dibuka, arus pengumpul tidak melebihi maksimum yang dibenarkan untuk jenis transistor yang dipilih. Itu dia ![]() .

.

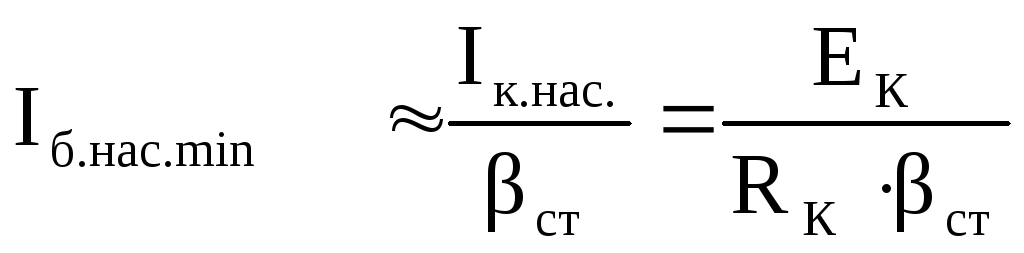

Pembukaan transistor yang boleh dipercayai disertai dengan peralihannya ke kawasan tepu, manakala arus I Knas mengalir dalam litar pengumpul. , ditakrifkan oleh hubungan  . Voltan U CE dalam mod tepu adalah berbeza untuk jenis transistor yang berbeza dan biasanya terletak dalam julat 0.08 ÷ 1 V. Arus asas minimum yang diperlukan untuk memastikan mod tepu ditentukan oleh ungkapan:

. Voltan U CE dalam mod tepu adalah berbeza untuk jenis transistor yang berbeza dan biasanya terletak dalam julat 0.08 ÷ 1 V. Arus asas minimum yang diperlukan untuk memastikan mod tepu ditentukan oleh ungkapan:

.

.

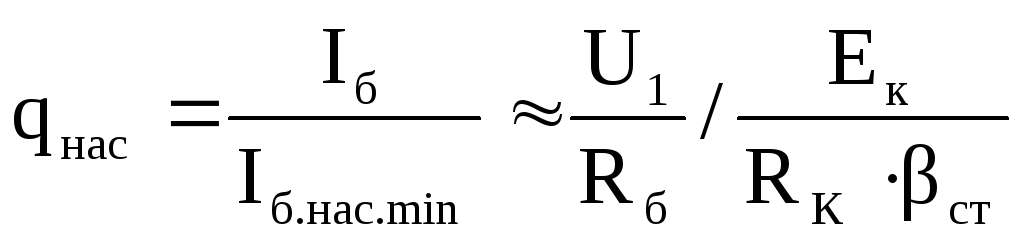

Kedalaman tepu dianggarkan melalui pekali tepu q us, yang menunjukkan berapa kali arus tapak sebenar lebih besar daripada nilai minimum arus asas yang diperlukan untuk memastikan mod tepu. Itu dia:

.

.

Dengan q dipilih, kita boleh mengira elemen utama dalam mod statik. Dalam berbuat demikian, seseorang harus dipandu oleh pertimbangan berikut. Mod tepu mesti disediakan untuk pelbagai keadaan transistor jenis yang dipilih pada julat suhu tertentu. Peningkatan arus asas dalam mod tepu mengurangkan nilai U CE, mengurangkan kuasa yang dikeluarkan dalam litar keluaran transistor, tetapi pada masa yang sama kuasa yang dikeluarkan dalam litar inputnya meningkat. Di samping itu, peningkatan dalam arus asas mengurangkan masa peralihan dari keadaan tertutup kepada keadaan terbuka (ke mod tepu), tetapi melambatkan masa transistor keluar dari mod tepu. Berdasarkan pertimbangan ini, pengiraan mengambil q us =1.5 ÷ 2.

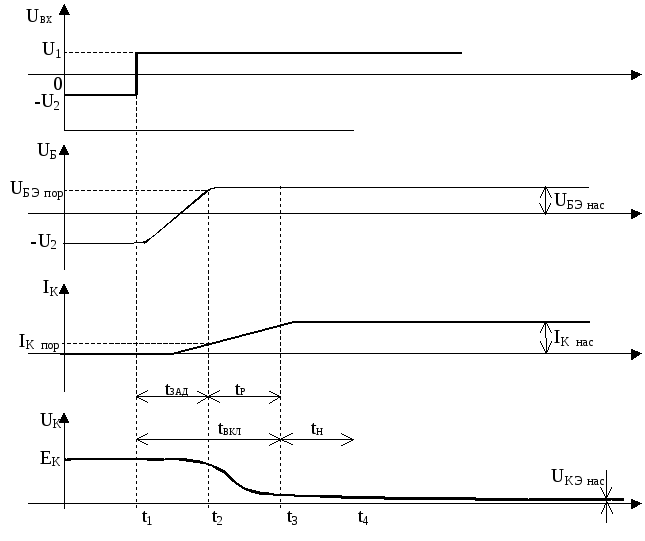

Kami akan mempertimbangkan mod operasi dinamik kekunci yang ditunjukkan dalam Rajah 9.11 pada gambar rajah pemasaan operasinya. Rajah 9.12 menunjukkan rajah pemasaan yang menerangkan proses menghidupkan suis transistor.

Rajah 9.11. Gambar rajah pemasaan untuk menghidupkan suis transistor

Apabila voltan pensuisan input digunakan, pengecasan semula kapasitans penghalang pemancar SE dan simpang S K pengumpul bermula, oleh itu, apabila pada masa t 1 voltan masukan berubah secara tiba-tiba, transistor kekal terkunci, kerana voltan pada kemuatan inputnya tidak boleh berubah. secara mengejut. Arus akan mula mengalir melalui rintangan asas, menukar U menjadi walaupun transistor itu sendiri terus kekal terkunci. Masa kelewatan boleh ditentukan secara anggaran oleh formula:

t 3 = dalam,

di mana in = R b (S E + S K), U bo - anjakan awal U b e - disebabkan oleh voltan masukan yang menonjol - U 2.

Nilai t 3 biasanya tidak besar. Oleh itu, masa ini sering diabaikan dalam pengiraan.

Apabila voltan U mencapai nilai ambang tertentu U menjadi ambang, transistor akan mula membuka kunci, membentuk bahagian hadapan isyarat keluaran t f. Dalam kes ini, arus pengumpul meningkat secara eksponen sehingga transistor memasuki mod tepu. Pada masa ini, U eq =U keluar menurun secara eksponen sehingga nilai U e us dicapai. .

Tempoh kelebihan negatif boleh ditentukan mengikut formula:

,

,

di mana a ialah pemalar masa litar asas,

- arus asas semasa peralihan kepada mod tepu.

- arus asas semasa peralihan kepada mod tepu.

Susunan magnitud hadapan negatif boleh dianggarkan dengan mempertimbangkan contoh biasa. Jadi, jika a =2 μs; st =50;  =1 mA;

=1 mA;  =5 mA, maka

=5 mA, maka  =0.2 µs.

=0.2 µs.

Jumlah masa hidup transistor ditentukan oleh jumlah t 3 + t f.

Bermula dari momen t 3, arus pengumpul, pemancar dan tapak secara praktikal tidak berubah, bagaimanapun, cas dalam tapak terus meningkat dengan pemalar masa H dan berakhir selepas masa t H = (2÷3) H.

Proses mematikan suis transistor digambarkan dalam Rajah. 9.12. dan bermula dari saat potensi kawalan negatif input (-U 2) digunakan (masa t 1), proses mematikan transistor berlaku dalam dua peringkat: penyerapan semula cas berlebihan (sehingga masa t 2) dan pembentukan kelebihan positif (sehingga masa t 3).

Caj yang terkumpul di dasar transistor terbuka tidak boleh hilang serta-merta dan untuk tempoh masa tertentu arus pengumpul tidak berubah. Dengan voltan penyekat yang cukup besar, masa penyerapan boleh ditentukan oleh formula

t p = H q kami Saya k.us. /( st I b),

di mana H ialah pemalar masa tepu; I b – lompat dalam arus asas pada saat suis mula dimatikan. Dalam selang penyerapan, arus asas (tanpa mengambil kira Ube) ditentukan oleh hubungan:

.

.

![]()

Rajah 9.12. Gambar rajah pemasaan untuk mematikan suis transistor

Semasa selang pembentukan hadapan positif, kepekatan pembawa nonequilibrium terus berkurangan, arus Ik berkurangan dengan ketara, dan voltan Uke meningkat. Pada penghujung masa turn-off (selepas masa t 3), arus pengumpul menjadi sama dengan arus asas, persimpangan pemancar dipincang ke arah yang bertentangan, arus asas dengan cepat berkurangan dalam magnitud dan menjadi hampir sama dengan sifar.

Dalam skim yang sedang dipertimbangkan, masa resorpsi t pelesapan adalah lebih lama daripada semua masa lain, jadi masa pereputan dan penubuhan boleh diabaikan. Perlu diingat bahawa lebih besar modulus arus pensuisan asas, lebih pendek masa resorpsi, dan lebih besar pekali tepu, lebih lama masa resorption.

Analisis kuantitatif proses sementara paling mudah dijalankan menggunakan pakej perisian untuk analisis mesin litar elektronik (contohnya Mikro - Cap V, dsb.)

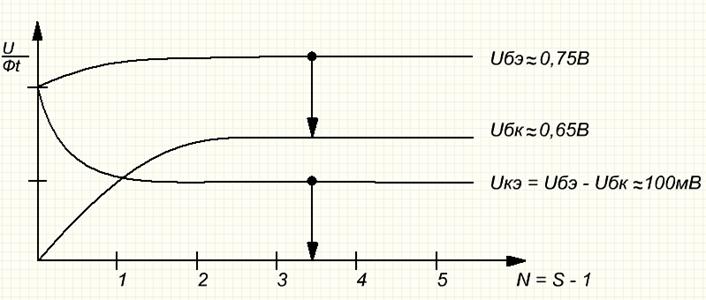

Salah satu cara untuk meningkatkan prestasi adalah untuk mengelakkan ketepuan transistor untuk mengurangkan masa penyerapan melalui penyelesaian litar khas. Dalam Rajah. Rajah 9.13 menunjukkan pilihan pelaksanaan bagi suis transistor tak tepu dengan maklum balas voltan negatif tak linear pada diod frekuensi tinggi.

Rajah 9.13. Pilihan pelaksanaan kunci tak tepu

Voltan pincang Ucm dalam litar sedemikian dipilih dalam julat 0.4÷ 0.6V. Skim ini berfungsi seperti berikut. Walaupun transistor cukup jauh dari kawasan tepu, diod VD ditutup oleh voltan E K. Di sempadan mod aktif dan mod tepu, voltan U KB ternyata hampir kepada sifar dan diod terbuka kerana U CM. Selepas ini, sebahagian daripada arus sumber isyarat input bercabang ke dalam litar diod, arus asas berkurangan dan transistor tidak memasuki mod tepu.

Dalam Rajah. Rajah 9.14 menunjukkan versi litar suis tak tepu di mana maklum balas negatif tak linear dilaksanakan melalui diod Schottky dengan voltan hidupkan kira-kira 0.25 V. Apabila menggunakan diod Schottky, tiada sumber pincang tambahan diperlukan.

Rajah 9.14. Suis tak tepu pada diod Schottky

Untuk menerangkan litar penukaran dan menyusun model matematiknya, cawangan dengan suis digantikan dengan rintangan aktif R (t), sifat perubahan masa diberikan oleh hasil darab rintangan suis dalam keadaan terbuka (besar dalam nilai, tetapi terhingga) oleh CF, berubah daripada sifar kepada satu pada saat-saat penukaran kunci. Mari kita terangkan perkara ini menggunakan contoh AC RO dua suis.

Untuk mengurangkan ralat yang diperkenalkan, peranti pensampelan dan storan mesti mempunyai laluan isyarat hadapan kecil dalam mod storan, tahap gangguan pensuisan yang rendah, suis terkawal analog tidak boleh mempunyai voltan baki, arus bocor yang ketara dalam keadaan terbuka, rintangan suis dalam tertutup keadaan mestilah minimum, kekutuban isyarat bertukar - mana-mana.

Bilangan tanda pekali pembahagian ditentukan oleh julat rintangan perintang yang mungkin, kerana, seperti yang dapat dilihat dari Rajah. 5 - 4, dalam, untuk tidak menjejaskan parameter baki kunci, rintangan yang lebih rendah hendaklah 1 - 2 urutan magnitud lebih banyak rintangan gk kunci tertutup, dan rintangan yang lebih besar ialah 2 - 3 susunan magnitud kurang daripada rintangan RK kunci terbuka.

Voltan input U disambungkan kepada beban menggunakan denyutan kawalan yang menukar transistor T1 dan T% kepada mod ketepuan dalam. Pada masa yang sama, rintangan kunci jatuh dengan mendadak, dan voltan U dibekalkan kepada output litar. Pada pemilihan yang teliti transistor, suis boleh menukar isyarat yang sangat kecil dengan ralat kira-kira 20 μV dalam julat suhu tertentu.

Arus terbalik suis simetri terbuka adalah sama dengan separuh perbezaan dalam arus terbalik transistor. Rintangan suis tertutup pada transistor germanium adalah kira-kira 10 ohm, pada silikon - 30 ohm. Apabila menggunakan transistor silikon, arus suis terbalik tidak melebihi 0 1 μA, transistor germanium - 5 μA.

Apabila suis K ditutup, rintangannya ditentukan oleh rintangan sentuhan peralihan; apabila suis K dibuka, rintangannya ditentukan oleh rintangan penebat litar. Dalam amalan, rintangan suis tertutup adalah sifar, dan rintangan suis terbuka adalah infiniti.

Pada hakikatnya, rintangan kunci tidak boleh berubah secara tiba-tiba dari sifar kepada infiniti, kerana voltan yang besar antara kenalan kunci akan menyebabkan percikan elektrik di antara mereka atau arka elektrik. Di samping itu, setiap gegelung mempunyai kapasitansi teragih di antara lilitannya, sama seperti terdapat kapasitansi antara kenalan mencapah kunci; oleh itu, proses pensuisan berlaku dalam tempoh masa yang terhad At, di mana proses peralihan yang mengalir dengan pantas dari saat permulaan hingga saat penghujung pensuisan selesai. Proses sementara ini, bergantung pada hubungan parameter, boleh menjadi aperiodik atau berayun dengan frekuensi yang sangat tinggi, dan perbezaan tenaga WM (- 0) - WM (0) dibelanjakan dalam rintangan litar, khususnya dalam rintangan antara kenalan utama, atau dalam sinaran pada sangat berfrekuensi tinggi. Kami tidak menganggap proses ini, yang berlaku pada masa At, di bawah idealisasi yang disebutkan di atas. Tetapi jika kita menganggapnya, maka pernyataan yang dirumuskan dalam § 9.4 akan menjadi sah. keadaan fizikal komutasi - invarian arus dalam gegelung dan voltan pada kapasitor, serta invarian tenaga yang disimpan dalam gegelung dan kapasitor.

Pada hakikatnya, rintangan kunci tidak boleh berubah secara tiba-tiba dari sifar kepada infiniti, kerana voltan besar antara kenalan kunci akan menyebabkan percikan elektrik atau arka elektrik di antara mereka. Di samping itu, setiap gegelung mempunyai kapasitansi teragih di antara lilitannya, sama seperti terdapat kapasitansi antara kenalan mencapah kunci; oleh itu, proses pensuisan berlaku dalam tempoh masa yang terhad At, di mana proses peralihan yang mengalir dengan pantas dari saat permulaan hingga saat penghujung pensuisan selesai. Proses sementara ini, bergantung pada hubungan parameter, boleh menjadi aperiodik atau berayun dengan frekuensi yang sangat tinggi, dan perbezaan tenaga WM (- 0) - 1 m (0) dibelanjakan dalam rintangan litar, khususnya dalam rintangan antara sesentuh kunci, atau dalam sinaran pada frekuensi yang sangat tinggi. Proses ini, yang berlaku pada masa A, tidak dipertimbangkan dalam idealisasi di atas. Tetapi jika kita menganggapnya, maka keadaan pensuisan fizikal yang dirumuskan dalam § 9 - 3 akan sah - ketakbolehubah arus dalam gegelung dan voltan pada kapasitor, serta invarian tenaga yang disimpan dalam gegelung dan kapasitor.

Pada hakikatnya, rintangan kunci tidak boleh berubah secara tiba-tiba dari sifar kepada infiniti, kerana voltan besar antara kenalan kunci akan menyebabkan percikan elektrik atau arka elektrik di antara mereka. Proses sementara ini, bergantung pada hubungan antara parameter, boleh menjadi aperiodik atau berayun dengan frekuensi yang sangat tinggi, dan perbezaan tenaga Ww (- 0) - W № (0) dibelanjakan dalam rintangan litar, khususnya dalam rintangan antara sesentuh kunci, atau dalam sinaran pada frekuensi yang sangat tinggi. Tetapi jika kita menganggapnya, maka keadaan pensuisan fizikal yang dirumuskan dalam § 9 - 3 akan sah - ketakbolehubah arus dalam gegelung dan voltan pada kapasitor, serta invarian tenaga yang disimpan dalam gegelung dan kapasitor.

Dalam litar DAC menggunakan penjana arus transistor, pensuisan arus boleh dijalankan dalam litar pengumpul. Dalam kes ini, rintangan utama tidak memperkenalkan ralat yang ketara disebabkan oleh rintangan litar yang tinggi. Walau bagaimanapun, kebocoran kunci yang terkunci boleh menyebabkan ketidaktepatan yang ketara. Jumlah kebocoran semua kunci terkunci tidak boleh melebihi separuh daripada arus tertib rendah.

Sebagai contoh, ketaklinearan rintangan suis apabila suis terbuka dan pergantungannya pada suhu boleh dilemahkan dengan menyambungkan perintang secara bersiri dengan suis, yang rintangannya jauh lebih besar daripada rintangan suis. Rintangan transistor kesan medan dalam keadaan terbuka ia biasanya berkisar antara 50 hingga 200 ohm. Termasuk perintang dengan rintangan 2 - 5 kOhm secara bersiri dengan transistor secara praktikal menghapuskan ralat yang disebabkan oleh tidak linear dan pergantungan rintangan suis pada suhu.

Menutup kekunci /C membawa kepada nyahcas pantas kapasitor. Kadar pelepasan bergantung pada rintangan kunci dalam keadaan tertutup. Laluan hadapan voltan gigi gergaji dalam litar ini terbentuk apabila suis dibuka, dan laluan terbalik terbentuk apabila suis ditutup. Oleh itu, untuk melaksanakan prinsip ini, penjana mesti mengandungi pengecas atau peranti nyahcas, kapasitor penyepaduan dan suis.

Dalam penukar delta-sigma, perintang dan rujukan voltan yang stabil juga boleh digunakan untuk menjana denyutan semasa, kerana titik penjumlahan sebenarnya pada potensi tanah. Dalam kes ini, adalah perlu untuk memastikan bahawa rintangan kunci tertutup adalah kurang daripada rintangan perintang dan perubahan dalam rintangan kunci tidak akan menyebabkan hanyut.

Transistor pergi dari mod cutoff ke mod tepu dan kembali bukan serta-merta, tetapi dalam tempoh masa tertentu. ini inersia transistor bipolar disebabkan oleh dua faktor utama: pengumpulan cas pembawa minoriti dalam pangkalan dan kapasitansi simpang pengumpul C dan pemancar C. Di samping itu, tempoh proses sementara suis transistor dipengaruhi oleh kemuatan beban DENGAN n .

Pengiraan tempoh proses sementara dalam suis transistor dijalankan menggunakan kaedah caj, berdasarkan fakta bahawa dalam pangkalan cas volum pembawa minoriti dikompensasikan, iaitu pangkalan adalah neutral elektrik.

Kaedah caj. Oleh kerana dalam tapak (p-region) pembawa minoriti ialah elektron, maka apabila u menjadi > U otn arus tapak i b (t) menentukan kadar pengumpulan elektron dq/dt di dalamnya (q ialah caj pembawa minoriti) dan mengimbangi penurunan q/t mereka akibat penggabungan semula (t ialah jangka hayat pembawa minoriti di pangkalan). Di samping itu, arus asas pergi untuk mengecas semula kapasitor "Sk dan Se apabila voltan pada peralihan berubah. Akibatnya,

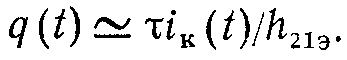

Jika arus kapasitif persimpangan pengumpul dan pemancar adalah kecil, maka persamaan (7.2) dipermudahkan:

dq/dt + q/t = i b (t) (7.3)

Dalam keadaan pegun, apabila dq/dt = 0,

q = tI b, (7.4)

iaitu, lebihan cas pembawa minoriti dalam pangkalan adalah berkadar dengan arus asas. Nisbah ini sah bukan sahaja dalam mod aktif, tetapi juga dalam mod tepu transistor.

Menggunakan persamaan (7.2) atau (7.3), seseorang boleh menentukan caj ruang pembawa minoriti dalam pangkalan sebagai fungsi masa. Walau bagaimanapun, apabila mengira litar nadi menggunakan transistor, kepentingan utama adalah dalam menentukan undang-undang perubahan dalam arus pengumpul.

Dalam mod aktif operasi transistor, dengan syarat taburan kepekatan pembawa cas minoriti dalam pangkalan adalah linear, terdapat hubungan yang, dengan penghampiran yang diketahui, memberikan hubungan antara cas pembawa minoriti dalam pangkalan dan arus pengumpul transistor:

(7.5)

(7.5)

Hubungan ini sah dalam mod pegun dengan ketepatan yang tinggi. Walau bagaimanapun, dalam rejim peralihan, tempoh yang sepadan dengan masa penyebaran pembawa di sepanjang pangkalan, sifat linear pengagihan pembawa minoriti di pangkalan dilanggar.

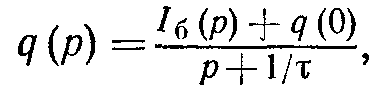

Dengan menyelesaikan persamaan (7.2) atau (7.3) dan menggunakan hubungan (7.5), seseorang boleh menentukan hukum perubahan arus pengumpul untuk arus tapak tertentu. Mari kita ubah persamaan (7.3) mengikut Laplace, kerana ini memudahkan prosedur penyelesaian untuk pelbagai keadaan awal:

(7.6)

(7.6)

di mana q(0) ialah nilai awal caj pembawa minoriti di pangkalan; R - pengendali Laplace.

Kelewatan hidupkan. Mari kita pertimbangkan proses menghidupkan suis transistor, dengan syarat bahawa pada masa /o pada inputnya voltan berubah secara mendadak daripada U b - kepada U b + (Rajah 7.5). Arus ditetapkan dalam litar asas

Walaupun voltan kawalan berubah secara mendadak, perbezaan potensi antara tapak dan pemancar, disebabkan terutamanya oleh kehadiran kapasitansi C e dan C k, meningkat kepada nilai U ot di mana transistor dibuka, tetapi tidak serta-merta, tetapi dalam masa tertentu. . Oleh itu, nadi arus pengumpul bermula pada saat masa, iaitu dengan sedikit kelewatan berbanding saat voltan buka kunci digunakan Selang masa t bangunan = t 1 – t 0 menentukan tempoh tahap kelewatan - masa, semasa pengecasan semula kapasitor S e dan S k berlaku . Oleh kerana arus kapasitif mengalir melalui transistor pada masa ini, litar setara suis transistor

nasi. 7.6. Litar Kunci Setara

nasi. 7 5. Proses sementara dalam kunci OE

![]()

n  dan peringkat tunda termasuk perintang luar dan kapasitansi simpang (Rajah 7.6).

dan peringkat tunda termasuk perintang luar dan kapasitansi simpang (Rajah 7.6).

Dalam suis transistor, biasanya Rb > Rk oleh itu, mengabaikan Rk kita memperoleh litar tertib pertama, proses sementara di mana ditentukan oleh hubungan

Apabila kapasitansi beban suis transistor Cn adalah sepadan dengan atau lebih besar daripada jumlah kapasitansi peralihan,

Selepas penggantian kita dapat

Peringkat kelewatan tamat apabila

sebab tu

sebab tu

Pembentukan bahagian hadapan. Apabila pada masa t 1 simpang pemancar dibuka, proses meningkatkan arus pengumpul bermula, disertai dengan penurunan voltan pengumpul. Arus pengumpul meningkat sehingga masa t 2 apabila transistor memasuki mod tepu. Dalam selang masa t 1 …t 2 . hadapan nadi semasa terbentuk. Tempoh hadapan t f = t 1 + t 2 boleh ditentukan daripada persamaan (7.6). Oleh kerana cas ruang awal q(0) = 0, dan

Menggantikan ungkapan (7.9) kepada (7.5), kita memperoleh:

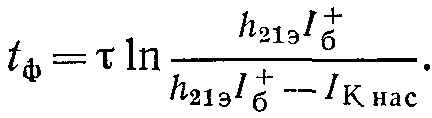

Oleh itu, kedua-dua cas volum pembawa minoriti di pangkalan dan arus pengumpul semasa pembentukan hadapan berubah mengikut undang-undang eksponen. Apabila i ke (t 2) = I ke dan caj pembawa minoriti di pangkalan mencapai nilai q (t 2) = tI kepada kami / h 21e, pembentukan hujung hadapan. Menggunakan hubungan (7.9), kita memperoleh formula untuk mengira tempoh hadapan

(7.11)

(7.11)

DAN  Daripada perhubungan yang terhasil ia mengikuti bahawa peningkatan dalam arus pensuisan asas membawa kepada penurunan dalam tempoh nadi hadapan arus pengumpul. Jika, semasa pembentukan hadapan, arus kapasitif adalah setanding dengan arus pengumpul transistor, maka untuk mengira t f dalam formula (7.11) adalah perlu untuk menggantikan t dengan t eq daripada (7.8).

Daripada perhubungan yang terhasil ia mengikuti bahawa peningkatan dalam arus pensuisan asas membawa kepada penurunan dalam tempoh nadi hadapan arus pengumpul. Jika, semasa pembentukan hadapan, arus kapasitif adalah setanding dengan arus pengumpul transistor, maka untuk mengira t f dalam formula (7.11) adalah perlu untuk menggantikan t dengan t eq daripada (7.8).

P  selepas transistor memasuki mod tepu, arus k dan voltan u k berhenti berubah, tetapi proses pengumpulan cas berterusan mengikut undang-undang eksponen mengikut ungkapan (7.9), namun, pemalar masa di sini berbeza: t us = (0.8... 0.9)t.

selepas transistor memasuki mod tepu, arus k dan voltan u k berhenti berubah, tetapi proses pengumpulan cas berterusan mengikut undang-undang eksponen mengikut ungkapan (7.9), namun, pemalar masa di sini berbeza: t us = (0.8... 0.9)t.

Memandangkan proses pengumpulan adalah bersifat eksponen, masa di mana caj pembawa minoriti mencapai nilai pegun boleh dikira menggunakan formula tus = (0.8...0.9)tus.

Ini melengkapkan proses menghidupkan suis transistor.

Prinsip operasi suis transistor

Peranti yang memproses isyarat berdenyut dipanggil peranti berdenyut. Antara pelbagai peranti nadi Kunci elektronik menduduki tempat yang menonjol. Tiada arus mengalir melalui suis terbuka yang ideal. Voltan merentasi suis tertutup yang ideal adalah sifar. Keadaan utama berubah di bawah pengaruh isyarat yang dibekalkan kepada satu atau lebih input.

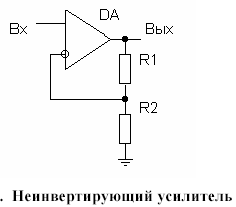

Paling aplikasi yang luas Sebagai suis elektronik, saya menemui lata transistor mengikut litar dengan OE dalam kelas gain D (iaitu dalam mod suis). Gambar rajah lata sedemikian ditunjukkan dalam Rajah. 15.2. Dalam mod suis, transistor boleh berada dalam salah satu daripada dua keadaan - dalam keadaan cutoff atau dalam keadaan tepu.

Dalam keadaan terputus, kunci dibuka. Hanya arus songsang kecil yang mengalir melalui transistor sayake O. Voltan di bahagian pengumpul-pemancar. Kuasa hilang dalam transistor Reput =sayake O ×

UKepada kecil kerana arusnya kecil.

Agar suis transistor berada dalam keadaan terbuka, adalah perlu untuk menggunakan voltan pincang negatif ke pangkalan, i.e. . Untuk tujuan ini, sumber berat sebelah tambahan sering digunakan - Yesm dan perintang R 2 (garisan bertitik dalam Rajah 15.2) Dengan sambungan ini, voltan pincang dicipta oleh dua sumber Yesm dan sumber semasa sayake oh, i.e.

. (15.1)

Percaya Ub< 0, получим

,

di mana

. (15.2)

Apabila transistor berada dalam keadaan tepu, kunci elektronik tertutup. Arus tepu mengalir melalui transistor, yang nilainya dihadkan oleh perintang RKepada. Mengabaikan voltan tepu rendah, kita boleh menulis

. (15.3)

Mod ketepuan dicapai pada arus asas  . (15.4)

. (15.4)

Seperti dalam mod cutoff, kuasa yang hilang dalam transistor dalam mod tepu adalah kecil kerana terdapat sedikit Un.

Arus asas dalam mod tepu dicipta oleh sumber voltan UVX Dan ESM. Dalam kes ini, bahagian pemancar asas transistor boleh dianggap litar pintas. sebab tu ![]() .

.

Keadaan tepu (15.4) mengambil bentuk ![]() . (15.5)

. (15.5)

Ungkapan (15.5) membolehkan anda menentukan nilai yang diperlukan R 1.

Pada masa ini, kunci elektronik dihasilkan dalam versi litar mikro. Sebagai contoh, litar mikro K564 KT3 mengandungi empat suis dwiarah dan direka untuk menukar isyarat analog dan digital dengan arus sehingga 10 mA.

1. Kekunci pada transistor bipolar............................................ ................................ 2

1.1.Maklumat am.............................................. ..... ................................................... .......... ....... 2

a) Kunci ideal .............................................. .......... ....................................... ................. ....... 2

b) Kunci sebenar .............................................. .......... ....................................... ................. ........ 2

c) Litar suis transistor................................................. ..... ................................... 3

1.2.Model transistor bipolar............................................. ....... ................................ 3

1.3.Mod pengendalian bipolar transistor npn.......................................................... 4

1. Mod aktif:............................................ ...... ................................................ ............ .. 4

2.Dalam mod cut-off:.......................................... ...... ................................................ ............ . 4

2.a) Dalam mod pemotongan dalam:............................................ .......... ................................ 4

2.b) Had pemotongan dengan mod aktif:...................................... ...... ............... 5

3.Dalam mod tepu:............................................ .... ................................................ 5

3.a) Had ketepuan dengan mod aktif:............................................ .... .......... 5

4. Mod songsang................................................ ...... ................................................ .. 5

1.4.Suis transistor dengan OE............................................ ........ .............................................. ..... 6

2. Parameter baki kunci pada BT......................................... ...... ................................ 9

2.1.Parameter baki transistor tertutup............................................ ......... ............. 9

2.2.Parameter baki transistor tepu............................................ ........ ..... 12

3. Suis transistor komposit................................................. ...... .................................... 15

3.1.???........................................................................................................................... 15

a) Jika transistor VT1 dikunci, maka................................... ..... ...................... 17

b) Jika transistor tepu, maka.................................... ..... ........................ 17

3.2.Transistor berbilang pemancar dalam mod pensuisan......................................... .......... ...... 19

a) Hidangkan voltan rendah ke mana-mana pintu masuk.............................................. ......... ............. 20

2. Menghidupkan transistor bipolar

2.1. Maklumat am

Suis transistor ialah peranti yang menukar (tutup atau buka) litar elektrik menggunakan isyarat input kawalan.

Penggunaan kunci - adalah asas litar mikro.

Kekunci mempunyai dua keadaan statik: tertutup dan terbuka.

1) Kunci ideal

|

nasi. 1.1.a: Skim utama | Keadaan tertutup(x.x.) rintangan utama Keadaan terbuka(x.x.) |

Peralihan ideal kunci dari satu keadaan ke keadaan lain berlaku serta-merta, iaitu tempoh proses sementara ialah "0".

2) Kunci sebenar

mempunyai rintangan terhingga http://pandia.ru/text/78/356/images/image009_52.gif" width="72 height=25" height="25">.

Dalam keadaan terbuka arus kecil mengalir dalam kunci sebenar..jpg" width="230" height="267">

nasi. 1.1.b: kunci OE

nasi. 1.1.c: Kunci OB

nasi. 1.1.g: Kekunci OK

perolehan arus dan voltan

bergantung kepada

Kemungkinan pengaktifan berurutan mereka bergantung pada sifat kekunci.

Transistor dalam kekunci elektronik boleh beroperasi dalam mod berikut:

· potongan;

· ketepuan;

· aktif;

· songsang.

- pekali suntikan;

- pekali suntikan;

http://pandia.ru/text/78/356/images/image020_35.gif" width="90" height="25">- pekali resapan;

Panggilan" href="/text/category/koll/" rel="bookmark">pengumpul boleh diabaikan;

http://pandia.ru/text/78/356/images/image023_32.gif" width="137" height="50"> - pekali pemindahan.

2) kesan modulasi lebar asas apabila voltan di persimpangan pengumpul asas tidak diambil kira (kecekapan pemancar tidak bergantung pada arus);

3) ketumpatan arus suntikan adalah rendah (tahap doping asas kekal malar dan rendah).

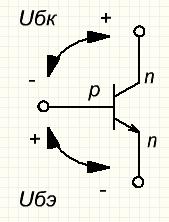

2.3. Mod pengendalian transistor n-p-n bipolar

Dalam mana-mana litar, tidak kira sama ada ia beroperasi dalam mod statik atau dinamik, transistor pada bila-bila masa beroperasi dalam salah satu mod berikut: aktif, potong, tepu, songsang.

1. Mod aktif:

Persimpangan pemancar dipincang ke hadapan, persimpangan pengumpul dipincang songsang. Kriteria mod aktif yang berpotensi n-p-n BT:

nasi. 1.3.a: ??? |

2. Dalam mod potong:

simpang pemancar dan pengumpul dipincang ke arah yang bertentangan..gif" width="64" height="25 src=">.

2.1) Dalam mod pemotongan dalam:

jika voltan menyekat pemancar dan simpang pengumpul dengan ketara melebihi potensi suhu.

Kriteria potensi:

http://pandia.ru/text/78/356/images/image028_24.gif" width="92" height="25">;

http://pandia.ru/text/78/356/images/image029_24.gif" width="92" height="25">;

2.2) Had pemotongan dengan mod aktif:

jika simpang pengumpul dikunci dan voltan pada simpang pemancar ialah “0”.

http://pandia.ru/text/78/356/images/image026_27.gif" width="64" height="25">;

3. Dalam mod tepu:

kedua-dua simpang dipincang ke hadapan (mod suntikan berganda).

http://pandia.ru/text/78/356/images/image026_27.gif" width="64" height="25">;

3.1) Had ketepuan dengan mod aktif:

jika simpang pemancar dipincang ke hadapan dan voltan pada simpang pengumpul adalah sifar:

http://pandia.ru/text/78/356/images/image031_21.gif" width="64" height="25">;

4. Mod songsang

dipanggil mod apabila simpang pemancar dipincang ke arah yang bertentangan, dan persimpangan pengumpul dipincang ke hadapan. Dalam kes ini, pengumpul berfungsi sebagai pemancar, iaitu, ia menyuntik pembawa ke dalam pangkalan, dan pemancar melaksanakan fungsi pengumpul.

http://pandia.ru/text/78/356/images/image026_27.gif" width="64" height="25">.

Dalam suis transistor, transistor boleh beroperasi dalam semua mod yang ditentukan. Jika BT beroperasi dalam mod potong atau dalam mod aktif pada arus pengumpul yang sangat rendah, maka ia adalah suis terbuka. Jika ia beroperasi dalam mod tepu atau mod aktif pada arus pengumpul tinggi, ia bertindak sebagai suis tertutup. Semasa peralihan dari satu keadaan ke keadaan lain, BT beroperasi dalam mod aktif.

2.4. Suis transistor dengan OE

Dalam peringkat penguat, BT beroperasi dengan isyarat kecil () dalam mod aktif. Dalam kunci - dengan yang besar.

Titik A- persimpangan garis beban dengan garis ciri pada sepadan dengan mod aktif.

Pada ketika inihttp://pandia.ru/text/78/356/images/image037_21.gif" width="197" height="25 src=">,

di mana http://pandia.ru/text/78/356/images/image039_22.gif" width="28" height="25 src=">.gif" width="79" height="25 src="> . Tanda “-” bermakna ia telah menukar arah yang bertentangan dengan yang ditunjukkan dalam rajah. Menukar arah adalah mungkin jika kekutuban isyarat input ialah (). Ini bermakna persimpangan pemancar adalah pincang songsang. Arah anjakan simpang pemungut tidak berubah dan kekal berbalik.

Oleh itu, pada titik "O" kedua-dua peralihan dianjak ke arah yang bertentangan dan titik ini sepadan dengan mod potong transistor.

Jika anda meningkatkan isyarat input, titik operasi akan melalui titik "A", arus asas akan meningkat dan titik kendalian akan bergerak di sepanjang garis lurus beban ke arah titik "H".

Apabila arus asas meningkat dan arus pengumpul meningkat, voltan pengumpul berkurangan:

![]() .

.

Selagi transistor beroperasi dalam mod aktif, arus pengumpul berkaitan dengan arus asas mengikut nisbah:

di mana http://pandia.ru/text/78/356/images/image045_18.gif" width="31" height="25">, dan arus pengumpul:

http://pandia.ru/text/78/356/images/image045_18.gif" width="31" height="25">-??? arus asas.

Voltan pengumpul:

Oleh itu http://pandia.ru/text/78/356/images/image049_15.gif" width="42" height="25 src=">adalah pecahan volt, dan

iaitu ia mencapai nilai maksimumnya.

Dalam mod tepu http://pandia.ru/text/78/356/images/image053_16.gif" width="28" height="25"> dan tidak bergantung pada parameter transistor.

Sambungan linear http://pandia.ru/text/78/356/images/image040_21.gif" width="25" height="25 src=">terputus. Sebaik sahaja mod transistor bergerak ke titik "H ”, arus pengumpul tidak lagi bergantung kepada arus asas Peningkatan arus asas tidak membawa kepada perubahan ketara dalam arus pengumpul, iaitu kedudukan titik operasi “H” secara praktikal tidak akan berubah.

Transistor telah bertukar kepada mod tepu.

Transistor berada pada had tepu apabila ..gif" width="64" height="25 src=">), dipanggil arus asas mengehad.

Kriteria tepu semasa:

Oleh itu, mod ketepuan ditentukan bukan oleh nilai mutlak arus, tetapi nisbah arus asas dan arus had asas.

Jika transistor beroperasi dalam mod tepu (), maka peningkatan membawa kepada peningkatan dalam kedalaman tepu.

Tahap ketepuan http://pandia.ru/text/78/356/images/image058_16.gif" width="162 height=56" height="56">

3. Parameter utama baki pada BT

3.1. Parameter baki transistor tertutup

a) Apabila nilai voltan penyekat di persimpangan pemancar berubah, iaitu, apabila kedalaman potong () berubah, arus asas tidak berubah dan tetap sama ![]() . Persamaan ini dipanggil kriteria pemotongan semasa.

. Persamaan ini dipanggil kriteria pemotongan semasa.

b) Kedua-duanya dalam mod potong dalam dan pada sempadan potong ![]() , arus pemancar.

, arus pemancar.

Litar setara kunci dalam mod potong boleh diwakili sebagai:

Tukar voltan keluaran

http://pandia.ru/text/78/356/images/image066_12.gif" width="104" height="25">;

http://pandia.ru/text/78/356/images/image068_11.gif" width="120" height="50 src=">.

Untuk mengekalkan mod potong apabila menukar daripada dan rintangan, adalah perlu untuk memenuhi syarat berikut:

clear:left; margin-left:20px;">

Ambang mematikan transistor ialah nilai bersyarat..gif" width="45" height="25">. Biasanya diterima.

3.2. Parameter baki transistor tepu.

|

a) Tegasan baki yang terkecil ialah . Oleh itu, adalah wajar untuk menggunakan suis supaya voltan baki ialah , iaitu, litar pilihan ialah suis dengan OE.

b) Kebergantungan tegasan baki pada tahap ketepuan

|

adalah voltan di persimpangan terbuka, ia meningkat dengan peningkatan.

berkurangan dengan peningkatan.

c) Dalam transistor sebenar, voltan baki bergantung kepada penurunan voltan merentasi rintangan isipadu lapisan. Pada arus yang lebih tinggi, penurunan voltan meningkat.

Oleh kerana lapisan "K" mempunyai rintangan dan panjang yang besar??? arus yang melaluinya adalah tinggi, sublapisan "n+" tersembunyi dimasukkan ke dalam reka bentuk transistor satah epitaxial.

d) Kebergantungan lemah voltan interelektrod pada "N" membolehkan kita membentangkan litar setara transistor dalam mod tepu dalam bentuk berikut:

http://pandia.ru/text/78/356/images/image086_7.gif" width="240" height="47 src=">.

Kerana voltan baki adalah kecil berbanding voltan bekalan kuasa 0 " style="border-collapse:collapse">

nasi. 2.2.d: Titik transistor-equipotential

4. Suis transistor komposit

4.1. ???

Jika beban kunci OE adalah kapasiti yang cukup besar, maka kunci tersebut mempunyai prestasi rendah.

Mari kita anggap bahawa transistor dalam litar kunci dimatikan serta-merta.

nasi. 3.1.a: Gambar rajah utama selepas bertukar (sebelum ini ia tepu) |

nasi. 2.2.a Penetapan voltan pada terminal transistor

nasi. 2.2.a Penetapan voltan pada terminal transistor nasi. 2.2.b: Kebergantungan tegasan baki pada tahap ketepuan

nasi. 2.2.b: Kebergantungan tegasan baki pada tahap ketepuan